The Crimson SDR from Per Vices is the future of software defined radio. The flexible wideband, high-gain platform comes equipped with four independent receive chains and four independent transmit chains, each capable of up to 200MHz of RF bandwidth up to 6GHz. At the core of the digital front, Crimson is powered by an Altera Arria V FPGA (5ASTMD3E3F31I3N) with an on-chip dual-core ARM Cortex-A9 processor with a web-based interface for controlling Crimson.

The Crimson SDR radio combines the latest advances into an SDR with a great deal of flexibility and processing power. The radio is housed in a relatively small enclosure for ease of integration with other systems. It handles a total operating frequency range of 100 kHz to 6 GHz using multiple signal channels and processors. It can tackle as much as 800-MHz bandwidth by means of four independently controllable receive channels and as much as 800-MHz bandwidth using four independently controllable transmit channels.

Frequency stability starts with an internal reference source based on a 10-MHz clock oscillator with ±5 ppb stability. The reference oscillator is designed to hold that frequency stability across a wide operating temperature range, enabling the radio to provide reliable communications under realistic operating conditions.

The receive section achieves small-signal gain of 67 dB. The high gain enables the SDR to detect even low-level signals, with a typical sensitivity of -110 dBm. At the high end of the dynamic range, the receiver provides a 1-dB power compression point (P1dB) of typically -11 dBm. It boasts a signal-to-noise ratio (SNR) as good as 73 dB with a spurious-free dynamic range (SFDR) of 55 dB at 200 MHz.

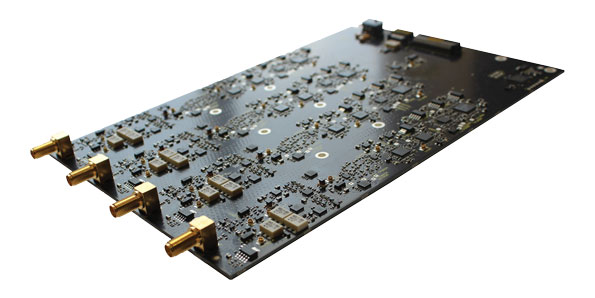

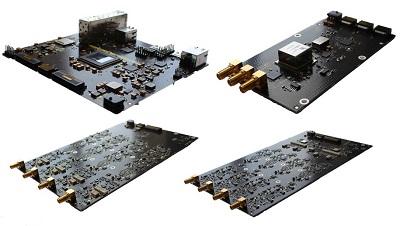

The SDR’s transmit section achieves maximum transmit power of +10 dBm at 6 GHz, with a typical P1dB of +14 dBm. The transmitter offers a spurious-free dynamic range of 61 dB from DC to 500 MHz. As the printed-circuit boards (PCBs) for the SDR’s receive and transmit sections show, the radio is based on a modular architecture which helps greatly simplify assembly during production and—later, if necessary—maintenance of different portions of the SDRs.

The SDR’s transmit section achieves maximum transmit power of +10 dBm at 6 GHz, with a typical P1dB of +14 dBm. The transmitter offers a spurious-free dynamic range of 61 dB from DC to 500 MHz. As the printed-circuit boards (PCBs) for the SDR’s receive and transmit sections show, the radio is based on a modular architecture which helps greatly simplify assembly during production and—later, if necessary—maintenance of different portions of the SDRs.

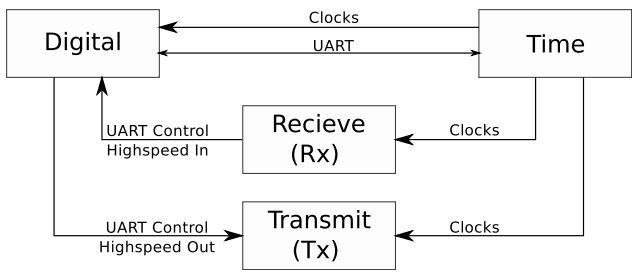

System Architecture

Crimson uses a highly modular design consisting of four boards, each connected using shielded, high speed cabling, to support its operation. The digital board provides an interface to the control and configures the receive, transmit, and time boards, along with high speed connections to the receive (Rx) and transmit (Tx) boards. Clock distribution extends from the Time board, which provides a very clean and stable clock distribution network. The default receive and transmit boards each comprise of four fully independent

channels.

Quick Specs

| 20Gbps using dual 10GigE | Up to 800MHz bandwidth | Includes web interface |

| Fully integrated, full duplex, RF frontend | 100kHz – 6GHz range SDR | Four RX and four TX chains |

| Four dual channel, 16 bit, 370 MSPS ADCs | Two quad channel, 16 bit, 2500 MSPS DAC | Digital down/up conversion on FPGA |

| Direct conversion quadrature transceiver | 10MHz, 10ppb, reference OCXO | Altera Arria V ST FPGA SoC |

| RX | TX | ||

| Gain | 67dB | Max Power | +10dBm @ 6GHz |

| SFDR | 55dB @200MHz | P1 dB | 14dBm |

| SNR | up to 73dB | SFDR | 61dB from DC to 500MHz |

| Sensitivity | -110dBm | ||

| P1 dB | -11dBm |